高速缓存(Cache)用来存放当前最活跃的程序和数据。

特点:

- 容量一般在几千字节到几兆字节之间;

- 速度一般比主存快5-10倍,由快速半导体存储器构成;

- 内容是主存局部域的副本,对程序员来说是透明的。

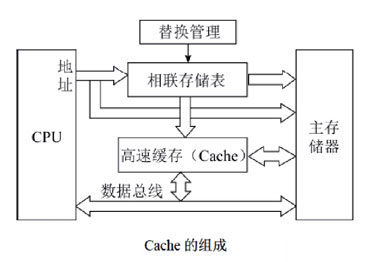

Cache一般位于CPU与主存之间,包括管理模块、由相联存储器构成的存储表以及小容量高速度存储器。

首先判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。

命中时直接对Cache存储器寻址;未命中时,要按照替换原则决定将主存的一块信息放到Cache存储器的哪一块里。

(一)高速缓存地址映像

方法 | 说明 | 优点 | 缺点 | |

1 | 直接映像 | 指主存的块与Cache块的对应关系固定。 主存中的块只能存放在Cache存储器的相同块号中,只要主存地址中的主存区号与Cache中的主存区号相同,则表明访问Cache命中。一旦命中,根据主存地址中的区内块号立即可得到要访问的Cache存储器中的块 块内地址就是主存地址中给出的低位地址。 | 地址变换很简单 | 灵活性差 |

2 | 全相联映像 | 主存与Cache存储器均分成容量相同的块。 允许主存的任一块调入Cache存储器的任何一个块空间中。进行地址变换时,利用主存地址高位表示的主存块号与Cache中保存的主存块号进行比较,若相同即为命中。根据块号就可知道要访问的是哪一块。 Cache存储器的块找到后,块内地址就是主存低位地址。 在变换时,当找到主存块号命中时,还必须知道主存的这一块存到了Cache哪一块里面。 | 主存的块调入Cache的位置不受限制,十分灵活。 | 无法从主存块号中直接获得所对应Cache块号,变换比较复杂,速度比较慢 |

3 | 组相联映像 | 是前面两种方式的折衷。 具体做法是将Cache中的块再分成组。 规定组采用直接映像方式而块采用全相联映像方式。 主存任何区的0组只能存到Cache的0组中,1组只能存到Cache的1组中,依此类推。 组内的块则采用全相联映像方式,即一组内的块可以任意存放。主存一组中的任一块可以存入Cache相应组的任一块中。 通过直接映像方式来决定组号,在一组内再用全相联映像方式决定Cache中块号。 由主存地址高位决定主存区号与Cache区号比较可决定是否命中。主存后面的地址即为组号。 |

(二)高速缓存替换算法

目标是使Cache获得最高的命中率

替换算法 | 说明 | |

1 | 随机替换算法 | 用随机数发生器产生一个要替换块号,将该块替换出去 |

2 | 先进先出算法 | 将最先进入Cache的信息块替换出去 |

3 | 近期最少使用算法 | 将近期最少使用的Cache信息块替换出去 |

4 | 优化替换算法 | 必须先执行一次程序,统计Cache替换情况。有了这样的先验信息,在第二次执行该程序时便可以用最有效的方式来替换。 |

(三)高速缓存性能分析

命中率→Cache性能→系统性能。

Cache设计目标:在成本允许条件下达到较高命中率,使存储系统具有最短的平均访问时间。

设Hc为Cache命中率,tc为Cache存取时间,tm为主存访问时间,则Cache存储器的等效加权平均访问时间ta为:

ta=Hc*tc+(1-Hc)*tm=tc+(1-Hc)(tm-tc)

假设Cache访问和主存访问同时启动,tc为Cache命中时访问时间,(tm-tc)为失效访问时间。在Cache不命中时才启动主存,则

ta=tc+(1-Hc)tm

在指令流水线中,Cache访问作为流水线中的一个操作阶段,Cache失效将影响指令流水。

(四)cache失效率

降低Cache失效率是提高Cache性能的重要措施。

当Cache容量比较小时,容量因素在Cache失效中占较大比例。

(1)降低Cache失效率方法

- 选择恰当块容量

- 提高Cache容量

- 提高Cache相联度

(2)Cache命中率与Cache容量关系

Cache容量越大,则命中率越高,随着Cache容量增加,其失效率接近0% (命中率逐渐接近100%)。

增加Cache容量,意味着增加Cache成本和增加Cache命中时间。

(3)多级缓存

在多级Cache计算机中,Cache分为一级(L1 Cache)、二级(L2 Cache)等,

CPU访存时首先查找L1 Cache,如果不命中则访问L2 Cache,直到所有级别Cache都不命中,才访问主存。

目前,CPU内Cache通常为二级结构,通常要求L1 Cache速度足够快,以赶上CPU主频。L1 Cache容量一般都比较小(几KB到几十KB);L2 Cache具有较高容量(几百字节到几兆字节),以具有足够高命中率。